☆ Yσɠƚԋσʂ ☆

- 12.2K Posts

- 12.8K Comments

5·5 hours ago

5·5 hours agoCompletely agree, and the fact that this is the narrative that’s being peddled means that most people have no idea what’s really coming.

2·6 hours ago

2·6 hours agoYeah, very much agree with all that. The decision making is very erratic. Although, I do think that attack on Iran was largely about cutting Asia and Europe off from the energy in the Gulf. While Venezuela and Greenland could be long term grabs where they don’t necessarily expect an immediate benefit. The big question is whether the US economy can handle the immediate shock.

3·6 hours ago

3·6 hours agoI’ve been using LLMs pretty extensively. These tools are effective, they can solve hard problems, and they allow me to work on a wider range of tasks than could before.

But, they’re also jagged in terms of functionality. When you work with a human, you can learn what their core competencies are, and then if you give them a task that falls within that domain, you can be reasonably sure they’ll finish it correctly. That’s not the case with LLMs. It might do one task brilliantly, and a next similar task, it just shits the bed on. And since it has no understanding of the task in a human sense, it can’t self correct, learn or improve. All its doing is stringing tokens together based on probability.

So, you need a human in the loop to review everything that it’s doing. Reviewing everything the model outputs takes a lot of time, hence actual productivity gains aren’t all that significant. Having an LLM will allow a backend developer to work on the frontend with fairly low friction for example, but they’re still going to build stuff roughly at the same pace.

Companies that try to replace humans with LLMs will soon find that they end up with a whole bunch of code that doesn’t actually work, and they have no hope of fixing. The fact that LLMs can produce a lot of code very quickly is precisely the danger because nobody knows what that code is doing, and it’s almost certainly not correct.

3·6 hours ago

3·6 hours agoI don’t really see how that helps the current crunch though. Any new oil development is going to take years to ramp up. By then the crisis will have already happened, and likely countries will have started mass switching to renewables from China.

5·10 hours ago

5·10 hours agoThat’s the beauty of Chinese state driven economy. The state can pour money into new technologies at a scale that no private business would ever do, which makes it possible to get to the point where new tech becomes commercially viable.

4·11 hours ago

4·11 hours agoI mean that fits given the US is a gerontocracy.

read all about it on your beloved wikipedia https://en.wikipedia.org/wiki/Democratic_centralism

literally every survey done in China by western orgs confirms that it is in fact a democracy, and one functioning better than any western attempt I might add

- https://www.newsweek.com/most-china-call-their-nation-democracy-most-us-say-america-isnt-1711176

- https://www.csmonitor.com/World/Asia-Pacific/2021/0218/Vilified-abroad-popular-at-home-China-s-Communist-Party-at-100

- https://www.bloomberg.com/opinion/articles/2020-06-26/which-nations-are-democracies-some-citizens-might-disagree

- https://web.archive.org/web/20230511041927/https://6389062.fs1.hubspotusercontent-na1.net/hubfs/6389062/Canva images/Democracy Perception Index 2023.pdf

- https://www.tbsnews.net/world/china-more-democratic-america-say-people-98686

- https://web.archive.org/web/20201229132410/https://en.news-front.info/2020/06/27/studies-have-shown-that-china-is-more-democratic-than-the-united-states-russia-is-nearby-and-ukraine-is-at-the-bottom/

7·23 hours ago

7·23 hours agoand looks like it’s cause of data centre water use too https://www.commondreams.org/news/aoc-data-centers-water

6·1 day ago

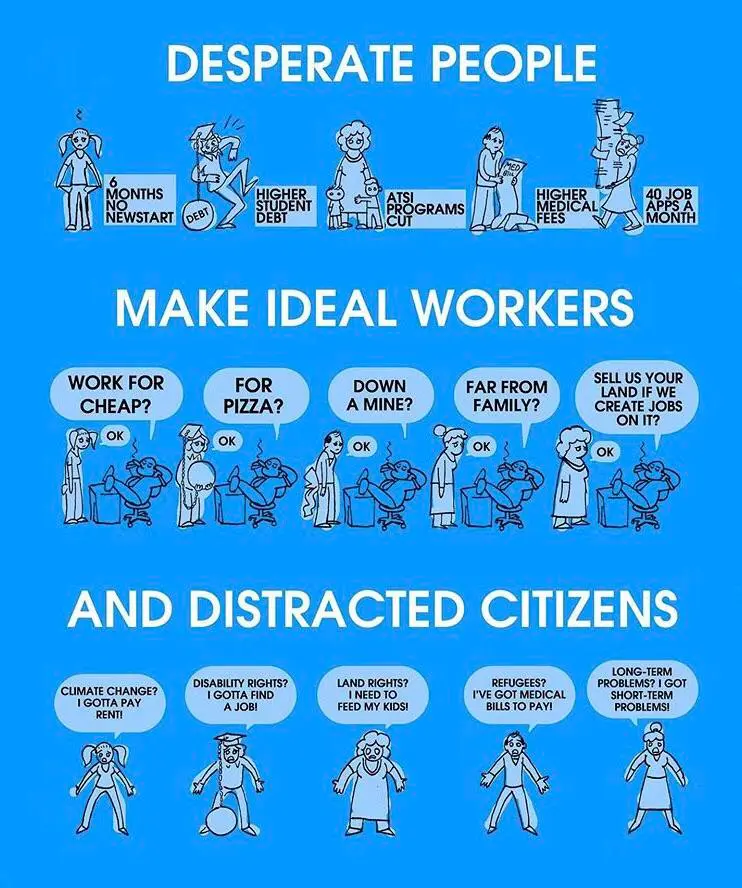

6·1 day agoyeah it’s not like they’re hiding it

12·1 day ago

12·1 day agoI mean we’ve seen how prices for Chinese solar and EVs dropped once production ramped up, I expect we’ll see the same with memory and eventually chips too.

Turns out if you start with basically nothing and strings just fall out. Turns out that you don’t need to assume strings exist at all. Four simple rules, two from quantum mechanics and relativity that everyone already accepts, plus the idea that physics stays consistent at insane energies and that nature picks the simplest possible math then the equations spit out the exact scattering amplitudes string theorists predicted decades ago. The Veneziano amplitude, the Virasoro-Shapiro amplitude, and the whole tower of massive spinning particles all just appeared automatically. Strings end up naturally appearing as an emergent phenomena in this framework. It important to note that this is not experimental proof since the energy scales are still stupidly out of reach, but the bootstrap math says if you want a universe that makes sense under these bare minimum rules then string theory is basically what you get.

25·1 day ago

25·1 day agoIt’s really frustrating to watch how people keep talking about how you just have to vote harder, when we can see a concrete example of how workers actually take power in Bolivia.

3·2 days ago

3·2 days agoBasically, the actual problem is with the capitalist system of relations and how automation is inevitably applied by the capitalists to harm workers.

3·2 days ago

3·2 days agoSame, AI haters really don’t realize just how far this tech has come in just the past year. I’ve had to work on frontend Js projects at work, and I’ve been lucky enough to avoid Js for most of my career. I have lots of experience programming, and I know how to structure applications, but I’m not familiar with Js stack, libraries, and syntax quirks. LLMs help me paper over all that and use it like any other language I’m already well versed in. Without LLMs, I would’ve had to spent literally months ramping up on Js ecosystem to do the work I’m doing now.

yup